研究テーマ / Research topic

制御システムのマルチコアプロセッサ実装時における並列度の向上を考慮した制御系設計に関する研究

| English ver. | Japanese ver. |

Embedded systems in industrial applications

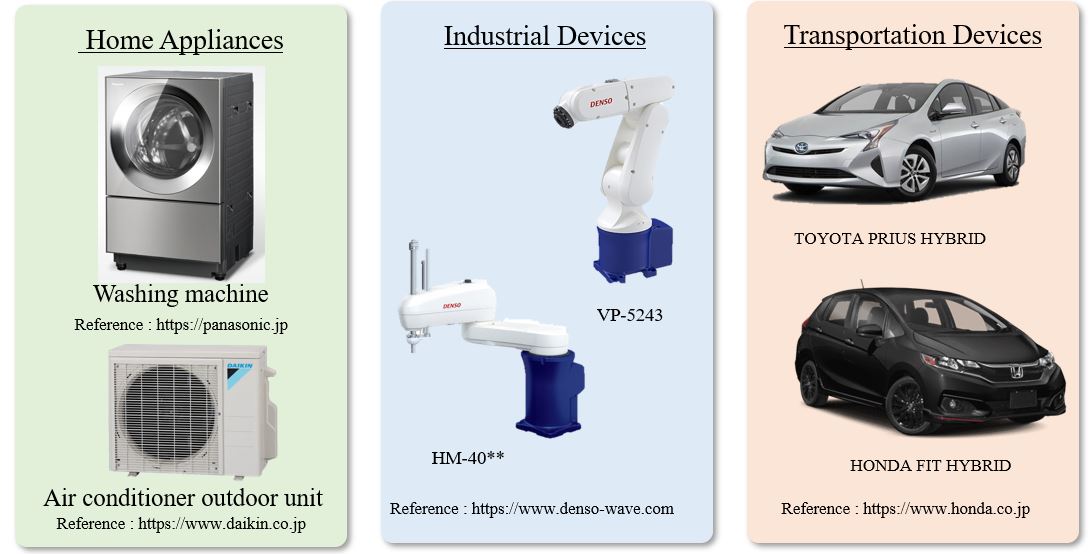

Embedded systems control many devices in common use today such as Home Appliances, Industrial Devices, Transportation Devices.

The range of applications for embedded systems is expected to become wider and larger in the future. In order to a high-performance, the high-quality device requires a large amount of program processing, so it is necessary to improve the performance of the calculator.

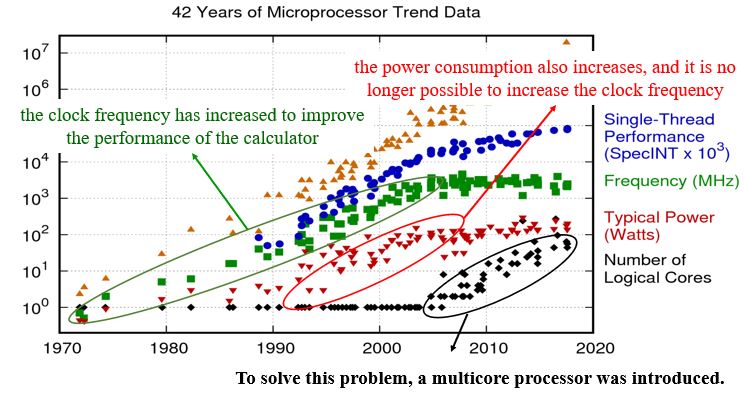

To improve the performance of the calculator a multicore processor was introduced.

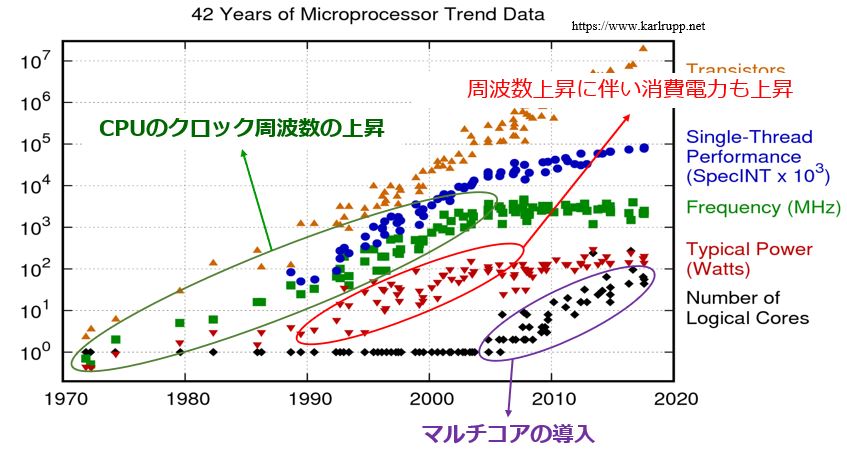

< https://www.karlrupp.net >

Until now, the clock frequency has increased to improve the performance of the calculator. However, as the clock frequency increases, the power consumption also increases, and it is no longer possible to increase the clock frequency. To solve this problem, a multicore processor was introduced.

Therefore, in recent years, the ability of calculators has been improved without increasing the clock frequency.

Development of Model-Based Parallelization technology

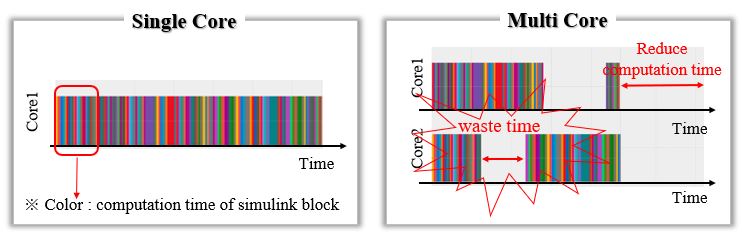

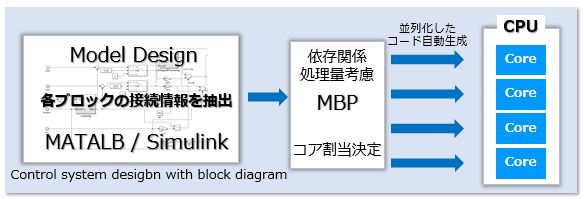

In order to use a multi-core processor efficiently, optimal parallelization of the program is required. However, it is difficult to parallelize a complex system to a detailed part with hands because of the heavy workload. To solve this problem, Model-Based Parallelization(MBP) has been proposed, which is an automatic parallelization technic for multi-core processors.

MBP (Model-Based Parallelization) is a tool that automatically generates parallel code for a highly reliable and high-performance multi-core environment by using a model designed by MathWorks®’s model design tool “Simulink®”.

By using the MBP, it is possible to perform delicate parallelization of control algorithms that are difficult to perform manually, and significantly reduce the work-time for parallelization.

Result of Parallelization using the MBP Tool

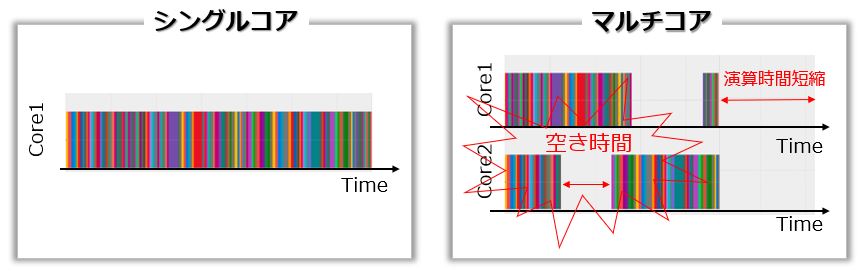

This result, applying MBP is one of the control algorithms is shown. Parallel processing with multicore can reduce computation time. As such, the reduction of computation time is realized because of the introduction of multicore. However, the effect of parallelization is limited due to wasted time as shown in this picture.

Causes of Waste Time and How to Improve Parallelization

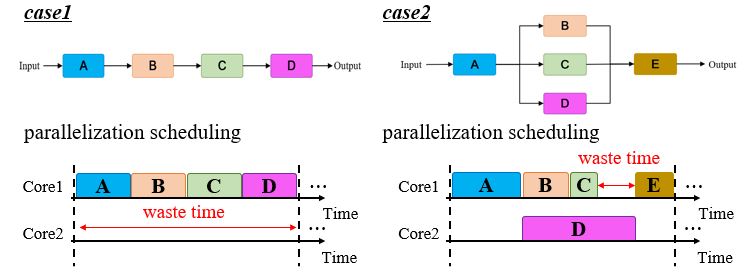

Why waste time occurs in parallelization?

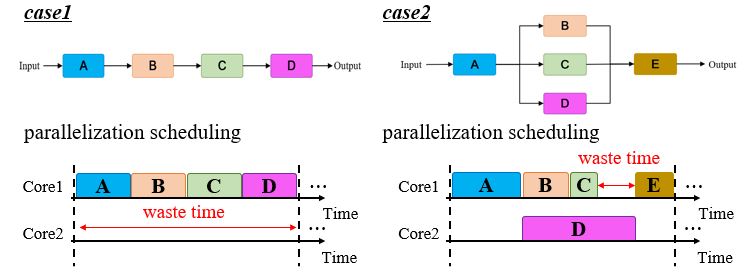

The next calculation can be performed only after the calculation in the previous block is completed.

As the figure shows, the next calculation can be performed only after the calculated in the previous block is completed. In other words, This waste of time is caused by an algorithm with a time constraint that has a fixed computational sequence.

It is difficult to parallelize in such an algorithm with a set calculation order. As a result, the multicore processor becomes low efficient.

How to Improve parallelization?

Case1 : A method of introducing Time-Delay A method of introducing Time-Delay has been proposed as one of the methods for improving parallelization and reducing computation time[2].

By inserting the Time-Delay, the computation of C, D can be performed using the value before 1 control cycle of A, B. Then we can confirm that parallelization is possible as shown in this figure. And that also reduces the computation time.

In the end, This method not only improves the degree of parallelization but also shortens the control cycle.

Case2 : A method of Multi-Rate system

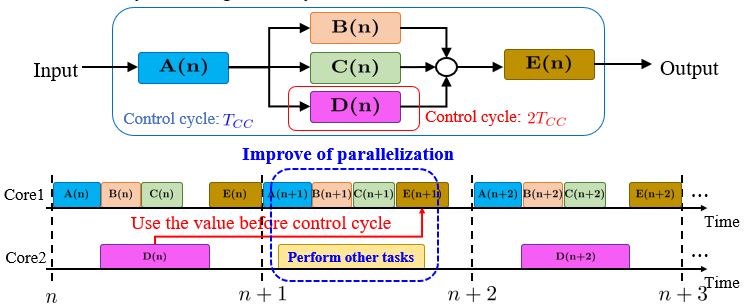

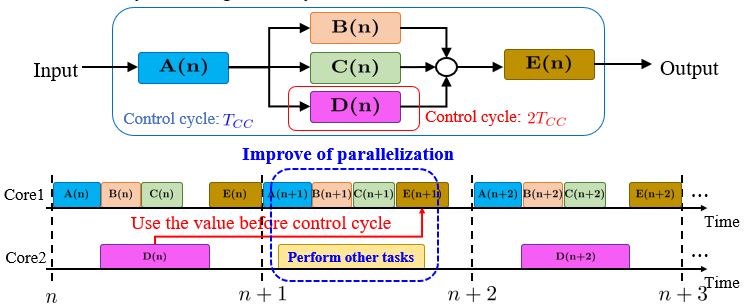

Another way to improve the degree of parallelization is a multi-rate system that changes some control cycles to long control cycles.

As shown in the figure, this approach allows some control periods to be twice as long as the current control period. Parallelization in this system, Eliminate wasted time using previously calculated values, Parallelization can be improved by processing other tasks that are independent of the current operation.

In the end, By using a multi-rate system, parallelization can be improved by eliminating wasted time and processing other operations at the same time.

However, these methods are expected to improve parallelization, these approach can make degrade the designed performance.

A Study on the Method of Utilizing Time-Delay Insertion

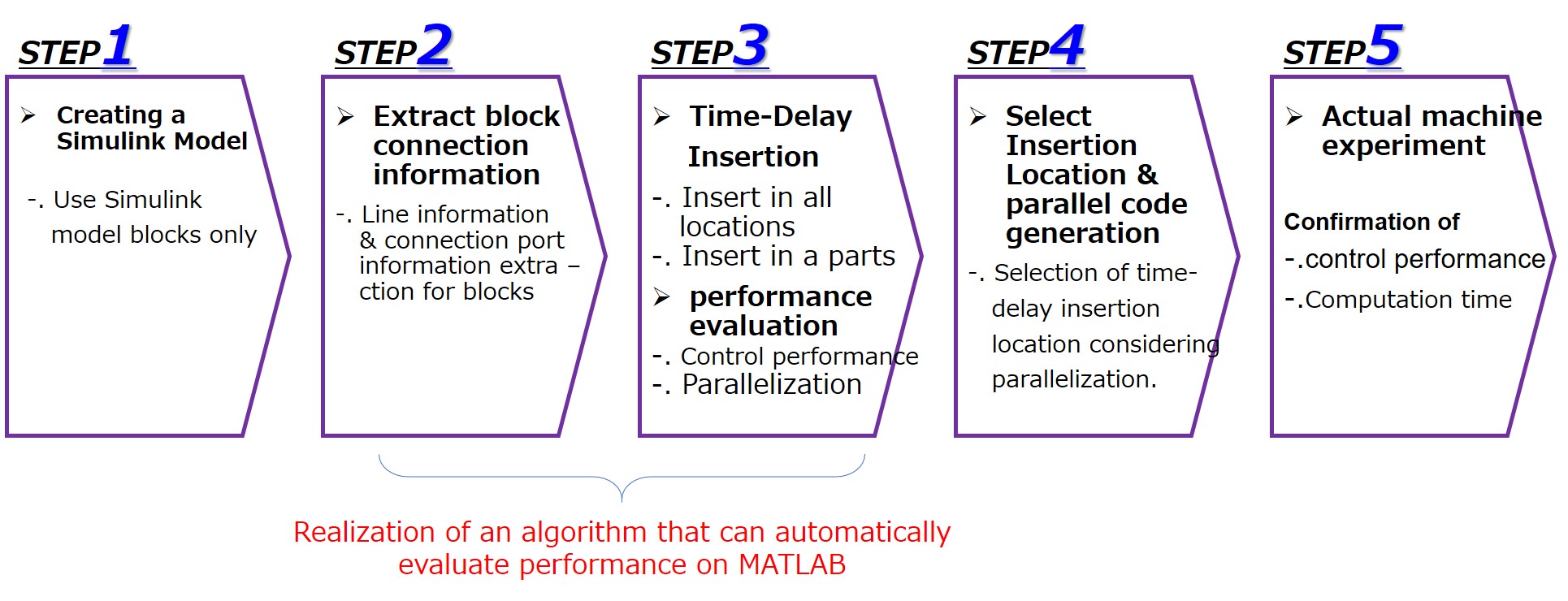

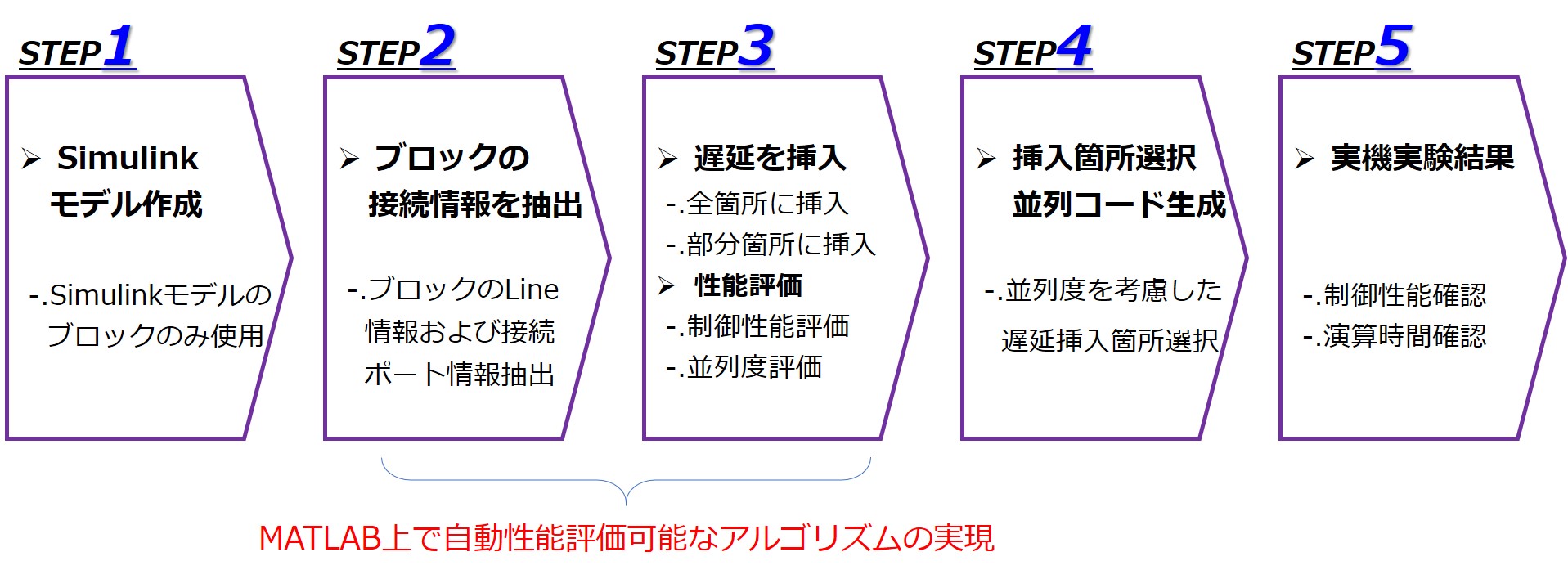

Because the parallelization and control performance is different for each part of the time- delay insertion, it is necessary to find the optimal location.

By proceeding with the research in the following flow, we will find the most suitable time-delay insertion location.

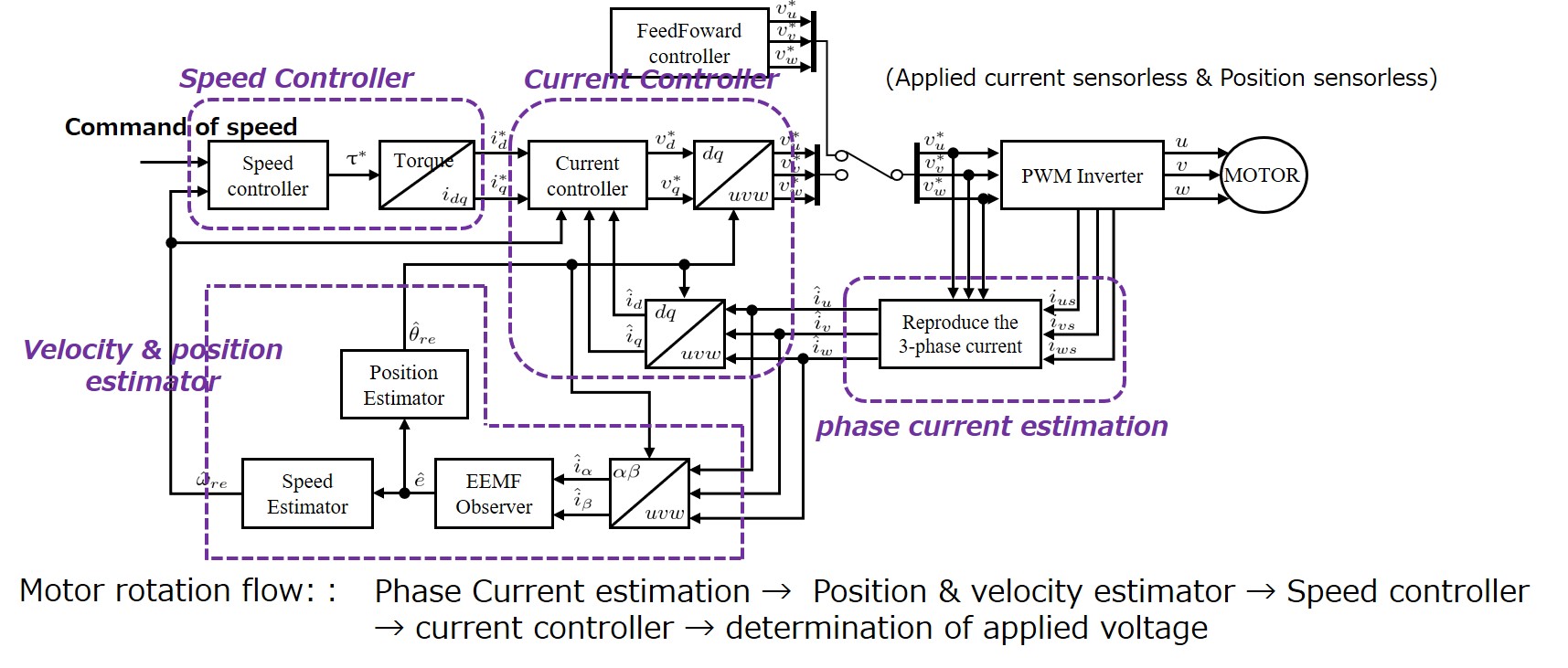

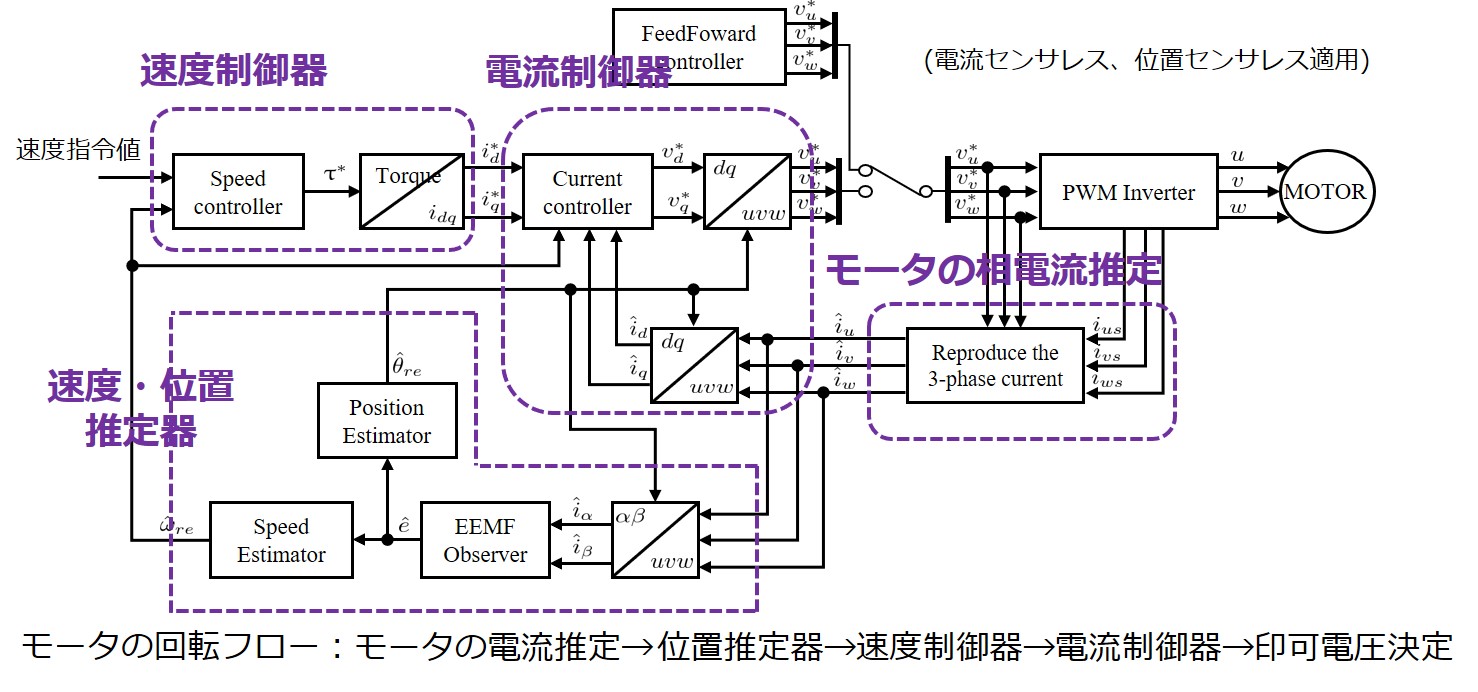

The evaluation target : Speed control system of the motor

A control system that starts with FF control (control method ①) and switches with vector control (control method ②)

-. It is required to strictly adhere to the set control cycle (tens to hundreds of μs).

-. Strict restrictions on processing orders due to a causal relationship.

Validation of the Evaluation System by Experiments

To verify the validity of this proposed method, We are considering the RC car Drive board shown in the following figure.

The main body configuration includes Renesas’s RH850/F1H(Dual-Core) microprocessor. A brushless motor, and a small embedded motor driver board that has the same functions as the brushless motor driver board.

Reference: https://www.hokutodenshi.co.jp

産業用アプリケーションの組み込みシステム

組込みシステムは、家電機器、産業機器、運輸機器などに広く使用されている。

組み込みシステムのアプリケーションの範囲は、今後さらに広くなると予想されます。高性能、高品質のデバイスを使用するには、大量のプログラム処理が必要になるため、計算機の性能を改善する必要があります。

そこでこれまでは、クロック周波数を上昇させて計算機の性能を向上してきました。しかし、この図のように周波数上昇に伴い消費電力も上がるのでクロック周波数の上昇が困難になってきました。そこで近年は、クロック周波数を上昇させず計算機の能力を上げるためにマルチコアが導入されています。

モデルベース並列化ツール(Model Based Parallelization tool)

マルチコアを有効に活用するために、マルチコアプロセッサに向けた自動並列化技術である、モデルベース並列化ツール(MBP)が提案されている。

MBP(Model Based Parallelization)は、MathWorks®のモデル設計ツール「Simulink®」によって設計されたモデルを使用して、信頼性が高く高性能なマルチコア環境向けの並列コードを自動的に生成するツールです。

このツールを用いることで,人の手では困難である,制御アルゴリズムの粒度の細かい並列化を行うことが可能です,さらに、自動で並列化を行うことで作業者の工数も大幅に削減することができます。

MBPを用いた並列化結果

この結果は, ある制御アルゴリズムをマルチコアプロセッサに実装した結果となります。この図に示すように並列処理が可能なマルチコアを用いることで演算時間の短縮が実現されています。

しかし, 空き時間が発生してしまい,並列化の効果が限定的となります。

空き時間の原因と並列度の改善方法

空き時間が発生する理由は?

並列化における空き時間は時間的制約の厳しいシステムで発生します。

すなわち、演算順序が決まっているシステムでは並列化することが難しいです。 結果として,そのようなシステムではマルチコアプロセッサの実行効率が低くなります。

並列化を改善するには?

方法1: 時間遅延を挿入

並列度を向上させるためのアプローチとして時間的制約を緩和する手法が検討されています。

時間遅延を挿入することにより、A、Bの1制御サイクル前の値を使用してC、Dの計算を実行できます。そうすると、この図に示すように、並列化が可能であることを確認できます。また、計算時間も短縮されます。したがって、この方法は並列化の程度を改善するだけでなく、制御サイクルを短縮もできます。

方法2: 制御周期変更

一部の演算周期を長周期に変更し,マルチレート系とすることで処理負荷を分散させる手法です。

以前の計算値を使用して空き時間を除いて、現在の演算に依存しない他のタスクを処理することで並列化を改善すとことができます。

しかし,これらの手法は並列度の向上が見込まれる一方で,時間的制約緩和によって制御系設計時の応答速度や安定性は保証されず制御性能が劣化する恐れがあります。

遅延挿入を活用方法の研究

遅延挿入の箇所毎に並列度及び制御性能が異なるため,最適な箇所を探す必要がある。以下のフローで研究を進めることで、最適な遅延挿入箇所を見つける。

評価対象はモータの速度制御系

この制御はFF制御(制御法①)で始動し一定速度に達するとベクトル制御(制御法②)で切り替える制御システムとなります。

この制御システムの特徴は設定される制御周期(数十~数百μs)を厳格(げんかく)に守ることが要求されており、因果関係により処理順序の制約が厳しいです。

今後の予定:実験による評価システムの検証

提案方法の妥当性を検証するために、次の図に示すRCカードライブボードを検討しています。

本体構成には、ルネサスのH850 / F1H(デュアルコア)マイクロプロセッサが含まれます。

また、ブラシレスモータおよびブラシレスモータドライバーボードと同じ機能を持つ組み込みシステムです。

Reference : https://www.hokutodenshi.co.jp